Hallo

@piotr_go Herzlichen Glückwunsch zum nächsten Teil des Projekts

Als absoluter Laie mit FPGA-Schaltungen habe ich ein paar Fragen, und ich bin noch vor dem Blinken der Diode

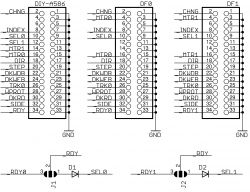

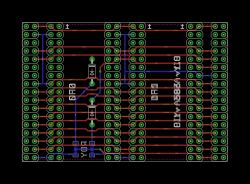

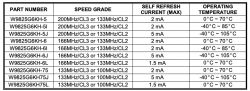

Nehmen wir an, ich möchte DIY-a586 mit z. B. Tango Nano 9k laufen lassen, woher weiß ich, dass die FPGA-Daten ausreichen, um die gegebene Peripherie zu simulieren?

Ist jedes FPGA in der Lage, Übertragungsleitungen wie HDMI oder Displayport i2s auf seinen I/O-Ports zu simulieren, wenn es dafür keine dedizierten Funktionsblöcke gibt?

Was ist der Fall, wenn die Stapelverarbeitungsdatei, die beispielsweise unter XC6SLX9 geschrieben wurde, beispielsweise an Cyclone I/II/III oder andere übertragen wird?

Wonach sollte man sich bei der Auswahl eines bestimmten FPGAs wirklich richten, abgesehen von der Anzahl der LUT-Elemente?

Nach meiner Überprüfung befinden sich Schaltungen mit mehr als 25.000 logischen Einheiten normalerweise bereits in BGA-Gehäusen. Daher meine Frage, könnte es nicht möglich sein, Funktionsblöcke in kleinere FPGAs aufzuteilen? z. B. Tango Nano 9k nur für Grafik und andere kleinere für die CPU und andere Peripherie?

An welchen Bus sollten diese Schaltungen angeschlossen werden, damit alles richtig funktioniert?